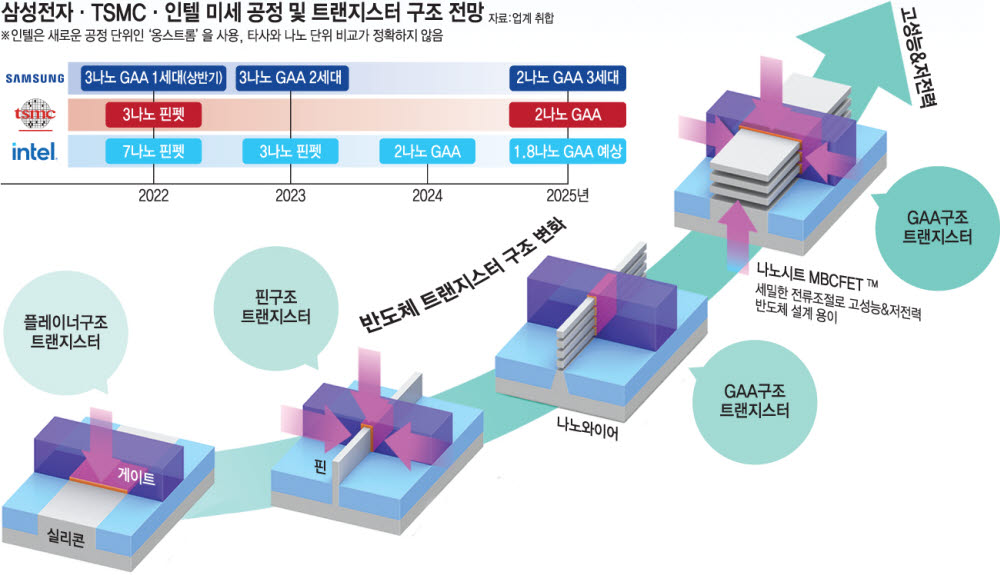

GAA(Gate-All-Around, 게이트 올어라운드)는 3nm 이하 초미세 반도체 공정에서 트랜지스터의 게이트가 채널을 360도 완전히 감싸는 차세대 구조로, 기존 FinFET의 물리적 한계(전류 누설)를 돌파해 성능 15%↑·전력 30%↓를 실현하는 2026년 반도체 산업의 핵심 기술입니다.

삼성전자가 2022년 세계 첫 3nm GAA 양산을 시작했고, 2026년에는 TSMC·인텔이 2nm 공정에서 GAA를 본격 도입하며 모든 첨단 파운드리 공정의 표준으로 자리잡습니다.

📐 GAA 구조: FinFET과의 결정적 차이

🔹 기존 FinFET (2011~2025년 주류)

- 구조: 게이트가 채널의 3면만 감싸는 핀(Fin) 형태.

- 한계: 5nm 이하에서 게이트 제어력 약화로 전류 누설 심화, 전력 소모 급증, 발열 문제.

- 확장성: 3nm가 물리적 한계, 그 이하는 동작 불안정.

🔹 GAA (2022년~현재)

- 구조: 게이트가 채널을 4면(360도) 완전히 감싸는 나노시트(Nanosheet) 적층 형태.

- 장점:

- 전류 누설 90% 감소: 게이트가 채널을 완전히 제어해 스위칭 정밀도 극대화.

- 전력 효율 30% 향상: 동일 성능 기준 전력 소모 30% 절감.

- 성능 15% 향상: 동일 전력 기준 동작 속도 15% 증가.

- 설계 유연성: 나노시트 폭·두께·적층 수 조절로 용도별 최적화 가능.

🏭 2026년 GAA 공정 경쟁 구도

1️⃣ 삼성전자 (GAA 선점자, 2026년 수율 안정화)

| 항목 | 내용 |

|---|---|

| 도입 시기 | 2022년 세계 첫 3nm GAA 양산 (선제 투자) |

| 기술명 | MBCFET™ (Multi-Bridge Channel FET), 나노시트 2층 적층 |

| 2026년 마일스톤 | 2nm SF2 공정 양산 본격화, 수율 60% 달성 목표 (3nm 50% → 2nm 60%) |

| 성능 | 3nm 2세대 대비 성능 5%↑, 전력 8%↓, 면적 5% 축소 |

| 주요 고객 | 퀄컴, 테슬라, AMD, 국내 팹리스 (TSMC 단가 상승으로 대체 수요) |

| 강점 | 3년 선행 도입으로 GAA 공정 노하우 축적, TSMC 대비 가격 경쟁력 (웨이퍼당 1.8만 달러 vs 2만 달러) |

| 약점 | 초기 수율 저조 (30~40%) 로 대형 고객사 확보 지연, 2026년 수율 60% 돌파가 승부처 |

2️⃣ TSMC (2026년 GAA 대량 양산, 독점적 지위)

| 항목 | 내용 |

|---|---|

| 도입 시기 | 2025년 2nm N2 공정에서 첫 GAA 적용 (삼성보다 3년 늦음) |

| 기술명 | Nanosheet Transistor, 2층 나노시트 + BSPDN (이면전원공급) 동시 적용 |

| 2026년 마일스톤 | 2nm 생산 능력 전량 예약 완료 (애플, 엔비디아, AMD 선점) |

| 성능 | 동일 전력 기준 성능 15%↑, 동일 성능 기준 전력 30%↓ (이론치) |

| 수율 | 80%+ (삼성 60% 대비 우위), 대량 공급 능력 입증 |

| 주요 고객 | 애플 (A20/M5), 엔비디아 (Rubin), AMD, 퀄컴 (플래그십) |

| 강점 | 압도적 수율·대량 생산 능력, 고객사 신뢰도, BSPDN 동시 적용으로 성능 극대화 |

| 약점 | 높은 단가 (웨이퍼당 2만 달러), 공급 물량 부족으로 대체 수요 발생 |

3️⃣ 인텔 (18A 공정으로 추격)

| 항목 | 내용 |

|---|---|

| 도입 시기 | 2025년 18A (1.8nm 급) 공정에서 GAA 적용 |

| 기술명 | RibbonFET™ (인텔 독자 GAA 명칭) + 파워비아 (BSPDN) |

| 2026년 마일스톤 | 18A 양산 시작, 파운드리 고객 3사 이상 확보 목표 (아마존, MS) |

| 성능 | 동일 전력 기준 성능 15%↑, 스위칭 속도 20% 향상 |

| 강점 | 미국 정부 CHIPS Act 보조금 (100억 달러+), IDM 2.0 전략으로 설계·생산 일관 공정 |

| 약점 | 파운드리 신뢰도 부족, 수율 검증 미흡 (2026년 초기 단계) |

⚙️ GAA 공정 제조 흐름 (6대 핵심 단계)

GAA 공정은 기존 FinFET 대비 공정 단계 30% 증가, 정밀도 10배 향상이 요구되는 초고난도 기술입니다.

| 단계 | 공정명 | 내용 | 핵심 장비 |

|---|---|---|---|

| 1 | 초격자 적층 | Si(실리콘)·SiGe(실리콘게르마늄) 교번 적층 (나노시트 전구체) | CVD (화학기상증착) |

| 2 | 핀 패터닝 | 포토리소그래피 + 식각으로 핀(Fin) 구조 형성 | EUV 노광장비 (ASML) |

| 3 | 더미 게이트 형성 | 임시 게이트 생성, 나노시트 위치 고정 | ALD (원자층증착) |

| 4 | 채널 릴리즈 | 핵심 단계: SiGe층만 선택적 식각해 나노시트 공중에 부유 | 선택적 식각 장비 |

| 5 | 게이트 적층 | 나노시트 4면에 HKMG (고유전율금속게이트) 균일 증착 | ALD (1nm 단위 정밀 제어) |

| 6 | 컨택 형성 | 소스·드레인·게이트 텅스텐 컨택 플러그 연결 | 식각·증착 장비 |

난이도: 채널 릴리즈 단계에서 나노시트 간 간격 5nm 이하 유지, 게이트 증착 시 0.5nm 두께 편차 허용 — 인간 머리카락 (80,000nm) 의 1/16,000 수준 정밀도.

📊 GAA 기술이 바꾸는 2026 반도체 산업

1️⃣ AI GPU 성능 50% 도약

- 적용: 엔비디아 Rubin (2nm GAA), AMD MI400, 구글 TPU v6.

- 효과: 동일 전력으로 AI 학습 속도 50%↑, 데이터센터 전력 30% 절감.

2️⃣ 모바일 AP 배터리 2배 연장

- 적용: 애플 A20 (2nm GAA), 퀄컴 스냅드래곤 8 Gen 5, 삼성 엑시노스 2600.

- 효과: 동일 배터리로 스마트폰 사용 시간 12→24시간, 발열 40% 감소.

3️⃣ 자율주행·로봇 실시간 추론

- 적용: 엔비디아 드라이브 손 (2nm GAA), 피지컬 AI NPU.

- 효과: 지연시간 5ms→2ms, 70B 파라미터 LLM 온디바이스 구동 가능.

⚠️ GAA 기술적 장벽과 해결 방향

| 장벽 | 내용 | 해결 방안 |

|---|---|---|

| 수율 저조 | 3nm 초기 수율 30~40%, 2nm도 60% 목표 (TSMC 80% 대비 열세) | 공정 단계 최적화, AI 기반 결함 검출, 3년 선행 경험 (삼성) 활용 |

| 패러시틱 커패시턴스 | 게이트·소스·드레인 간 기생 용량 증가로 고속 동작 저하 | BSPDN (이면전원공급) 동시 적용, 배선 구조 3D 재설계 |

| 공정 비용 급증 | EUV 3~4회 노광, ALD 100회 이상 증착으로 단가 50%↑ | 하이퍼 NA EUV (2027년) 도입으로 노광 횟수 감소, 장비 국산화 (한국) |

| 설계 복잡도 | 나노시트 폭·두께·적층 수 최적화 난이도 극상 | AI 기반 DTCO (Design-Technology Co-Optimization), EDA 툴 고도화 |

🇰🇷 한국 GAA 기술 경쟁력 (2026)

✅ 강점

- 세계 첫 GAA 양산: 2022년 3nm 선제 도입으로 3년 선행 노하우 보유.

- MBCFET™ 독자 기술: 나노시트 2층 적층, 폭·두께 최적화 설계 유연성.

- 2nm 수율 안정화: 2026년 수율 60% 달성 시, TSMC 대안으로 퀄컴·테슬라·AMD 수주 기대.

⚠️ 도전 과제

- 대형 고객사 부재: 애플·엔비디아 등 빅테크 수주 실패, 2026년 1~2사 확보 필수.

- 장비·소재 의존도: EUV (ASML), ALD (응용재료) 등 핵심 장비 90% 이상 수입.

- 인력 부족: GAA 공정 전문가 2,000명 부족, 정부·기업 양성 프로그램 확대 필요.

💡 2026년 GAA 투자·사업 전략 시사점

- 수율 60% 돌파가 승부처: 삼성전자의 2nm 수율이 60%를 넘어서면 TSMC 독점 구도 붕괴, 파운드리 시장 재편 시작.

- BSPDN 동시 적용 필수: GAA 단독으로는 성능 향상 한계, 이면전원공급 (BSPDN)과 결합해야 15% 성능·30% 전력 효과 실현.

- 장비·소재 국산화 기회: 한미반도체, 테스, 주성엔지니어링 등 GAA 특화 장비 기업 수혜 예상.

- DTCO·시스템 최적화: 단순 미세화 경쟁 종료, 설계·공정·패키징 통합 최적화 능력이 경쟁력 결정.

한 줄 요약: GAA는 3nm 이하 반도체 공정의 생존 필수 조건으로, 2026년 삼성전자의 수율 60% 돌파 여부가 파운드리 시장 2강 구도 (TSMC·삼성) 성패를 가를 것입니다.